The difference between FireWorld2 and FireWorld with a capital W like in WireWorld is that two red photon/electron cells may be either in a "2a" or "2k" position to give birth next to 2 or 3 wire cells, logically matching the underlying 03ajkr/2ak/3 rule. In Fireworld2 they may only be in the orthogonal 2a position. The newer Izhora 2b computer works with both rules, while the display of the original model relies on a reaction that does not work in FireWorld and requires Fireworld2. There is a variety of FireWorld called FireWorld7, slightly modified by adding S7 (03ajkr7/2ak/3), which turns blocks into cool p3 guns; the computer works identically under this variant and changes of any natural patterns are unlikely. All my further development focuses on FireWorld and machines with a 256x128 display.

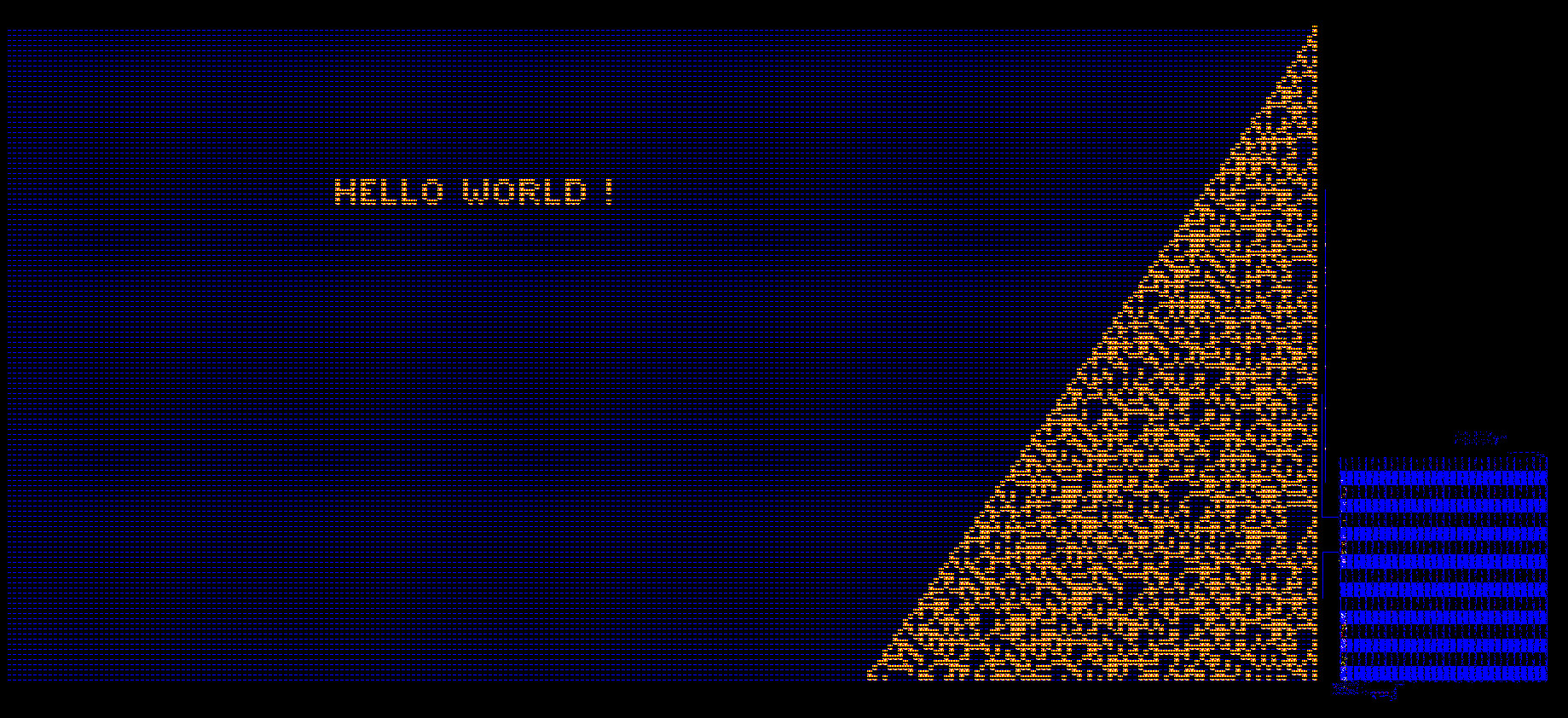

It took me about a year to build a computer in Fireworld2. Yesterday it successfully passed some tests and performed its "Hello World" program!

The current basic version, Izhora 1, has 256k of 32-bit word-addressable XOR-writable RAM, a 32-bit accumulator, a 16-bit program counter and a 128x64 graphic display. It has only one operation: a variety of Subleq known to be Turing-complete. On each cycle, the CPU reads a 32-bit word from the RAM and interprets its 16 highest bits and an absolute jump address and the lower 16 bits as an operand address. The accumulator is then subtracted from the operand; the result is stored in both the accumulator and the operand. If the result was zero or negative, the CPU branches to the jump address; otherwise it proceeds to the next instruction.

As simple as it is, Subleq systems are known to be practical. Some guy even wrote a full-fledged OS with a C-like compiler for an emulated 64-bit Subleq computer! Playing with it and with my own emulators of OISC (one instruction set computers) convinced me that Subleq is totally usable, somewhat similar to some real-life machines like PDP-8, although things like arbitrary bit manipulations or multiplication may require loops with hundreds of operations.

The RAM has a NUMA architecture. Cells located close to the CPU are accessed about 4 times faster than the furthest ones. The display memory starts at #0400. Note that since the machine was 32-bit addressing, #100 means 1024, not 256 bytes. The lowest 4k of the memory should be used for common library functions and variables.

The emulator, written in Common Lisp, is currently in pre-alpha stage (usable though). I hope to find time to write a Python as well as, perhaps, a C and Java version. An assembler and scripts for coding the actual machine in Golly are yet to be written. Some work has been already done toward a new version of the computer that will have, hopefully, RISC features implemented by mapping some jump addresses to other operations, optional relative addressing mode, several registers with an advanced ALU, and a script-driven emulated keyboard. If I ever find time for this...

Although the computer is fully operational, each operation takes about 40,000 generations on average. Programs longer than 10-20k will inevitably slow down hashlife. Don't expect to see more than 10 operations per second. The only way to run programs reasonably fast on Golly would be by a custom simulator script yet to be written.

By the way, Izhora is a river in outskirts of St. Petersburg, named after an ancient Finno-Ugric nation indigenous to the area.

Github repository:

https://github.com/yoelmatveyev/Izhora

"Hello World":

https://github.com/yoelmatveyev/Izhora/ ... _world.rle

The RAM uses p3 electron/photon streams and is very compact, approaching the theoretical limit of 1 bit per 6 cells (in practice, about 1 bit per 8 cells, because each 256-byte/64-word segment contains a controller). P6 is used for the CPU, because it can be crossed over with the dense p3 data and because p6 seems to be the minimum for flip-flops used in the adder and subtractor.

Besides the memory, this computer uses only stable asynchronous logic, which largely eliminates the timing issues. Clocks inside various parts turn automatically off after processing a stream of bits. All data outside of the pulsating memory wiring is encoded by a pilot bit indicating an incoming data stream, kind of like in a modem. A single photon means 0, unless it's used in something like a plain toggle flip-flop. Serial logic also eliminates the need for extensive bus wiring.

Some parts used in this project (to play, remove the dots blocking the p6 guns):

32-bit adder:

Code: Select all

x = 303, y = 138, rule = Fireworld2

29$66.C.C.C.C.C.C$79.C$171.C$62.C7.A.A.A4.C61.C29.C6.C3.C.C$62.C16.C

95.C2.C$64.C14.C3.C54.C3.30C10.C2.13C.C$78.2C59.4C14.C17.C2.C8.C$61.C

2.C6.C64.C.C.C16.C13.C10.C.C2.C$60.3C.C13.C2.3C.C49.C19.2C8.C5.C3.C2.

C8.2C.2C$71.2C.C3.3C.C51.C20.C8.C13.C10.3C$78.C6.C49.C.C15.2C9.C3.C

21.C$57.C21.C5.C48.C2.C6.C3.C.C13.C3.C22.C$69.C4.C3.C62.C2.C19.C7.C

18.C$21.CB34.C11.C4.C2.C.C54.4C10.C2.3C.14C4.7C11.C$21.AC34.C8.C15.C

6.C51.C2.C8.2C7.C9.C$22.C2.BA4.BA3.C28.C2.2C3.2C2.C4.C6.C36.C2.C7.C

10.C.C2.C14.C10.C9.C$25.BA4.BA53.C38.C3.C6.2C3.C2.C8.2C2.C6.C3.C10.C

6.2C.C.2C$22.C34.C20.C.3C4.3C43.C2.C7.C8.C3.C6.C$57.C12.10C6.C12.C2.C

13.C8.5C4.2C.C23.C2.C$82.C6.C8.C3.C6.C3.C2.C9.2C5.C20.4C4.4C2.C$57.C

12.C11.C6.C16.C2.C10.C.C6.C31.C3.2C.C21.A$71.C26.5C10.C2.C12.C23.C3.C

7.C$67.C17.C7.C12.C2.C10.C2.4C6.C6.C12.2C2.C7.C2.C22.C.C$57.C8.C18.C

7.C4.C3.C10.C2.C16.C3.C2.C4.C7.C11.C21.C5.C$89.C9.C2.C3.C2.C6.C3.C.C

30.C11.C$57.C8.20C4.4C15.C15.9C2.C.3C4.C18.C19.C8.C$22.C34.C31.C2.C

52.C39.9C$25.BA4.BA3.C48.C6.C4.C27.C7.C3.C11.C3.C3.C3.C31.C$22.C2.BA

4.BA30.C2.2C3.2C2.C3.2C4.C40.C6.C14.C3.C3.C3.C$21.AC34.C6.C16.C10.C4.

C50.C3.C3.C3.C25.C.2C12.C6.C$21.CB34.C9.C4.C2.C.C3.2C14.C43.2C5.C3.C

3.C3.C41.C6.C$67.C4.C3.C4.C.2C55.C.C5.C3.C3.C3.C45.C$57.C19.C7.2C53.C

.C5.C3.C3.C3.C7.C21.C6.6C4.3C$76.C8.C.78C3.C19.C.C15.C$69.2C.C3.3C85.

C37.C$58.3C.C13.C2.2C83.5C19.3C11.C$59.C2.C6.C$76.2C$62.C14.C$60.C16.

C$60.C7.A.A.A4.C2$77.C$64.C.C.C.C.C.C!Code: Select all

x = 296, y = 98, rule = Fireworld2

22$123.C.C.C.C.C.C$136.C2$119.C7.A.A.A4.C$119.C16.C$121.C14.C$135.2C$

118.C2.C6.C$117.3C.C13.C2.2C90.5C19.3C11.C$128.2C.C3.3C8.C.19C.C61.C

37.C$14.C120.C8.C.2C19.64C3.C19.C.C15.C$14.BC100.C19.C7.2C60.C.C5.C3.

C3.C3.C3.C3.C21.C6.6C4.3C$14.AC3.B.C104.C4.C3.C4.C.2C62.C.C5.C3.C3.C

3.C3.C41.C$19.B77.C18.C9.C4.C2.C.C3.2C9.C11.C43.2C5.C3.C3.C3.C3.C37.C

6.C$15.C81.C18.C6.C16.C11.C10.C50.C3.C3.C3.C3.C21.C.2C12.C6.C$97.C24.

C2.2C3.2C2.C3.2C4.C7.C4.C.C32.C6.C14.C3.C3.C3.C4.C$144.C3.C3.C6.C3.C

27.C7.C3.C11.C3.C3.C3.C31.C$97.C18.C35.C58.C39.9C$116.C8.20C2.C.4C5.

2C15.C15.9C2.C.3C4.C18.C19.C8.C$51.C11.C7.C79.C3.3C7.C2.C3.C2.C6.C3.C

.C30.C11.C$62.C8.C44.C8.C18.C3.C5.C4.C4.C3.C10.C2.C16.C3.C2.C4.C7.C

11.C21.C5.C$14.C36.C23.C50.C12.C4.C14.C12.C2.C10.C2.4C6.C6.C12.2C2.C

7.C2.C22.C.C$14.BC35.C10.10C4.4C50.C4.C4.C15.C7.5C10.C2.C12.C23.C3.C

7.C$14.AC4.C54.C.C.2C2.C4.C27.C12.C6.C3.C6.C24.C2.C10.C.C6.C31.C3.2C.

C21.A$57.C2.2C9.C8.2C6.C51.C2.C3.C16.C3.C6.C3.C2.C9.2C5.C20.4C4.4C2.C

$15.C35.C6.C8.C3.C20.C.C21.C12.8C3.C24.C2.C13.C8.5C4.2C.C23.C2.C$51.C

9.C12.2C.C3.8C4.8C5.C6.C2.C19.5C3.4C51.C2.C7.C8.C3.C6.C$61.C5.C24.C

13.C6.C26.C2.2C46.C3.C6.2C3.C2.C8.2C2.C6.C3.C10.C6.2C.C.2C$51.C13.3C

7.C.C10.C21.C13.C2.2C3.2C2.C5.C4.C44.C2.C7.C10.C.C2.C14.C10.C9.C$65.

3C9.C10.C12.6C4.3C2.C8.C19.C.C59.C2.C8.2C7.C9.C$65.2C14.C28.C5.C11.C

4.C2.C.C61.4C10.C2.3C.14C4.7C11.C$81.C2.2C15.C4.C21.C4.C3.C69.C2.C19.

C7.C18.C$67.12C5.2C6.C.C6.2C3.C9.C21.C5.C55.C2.C6.C3.C.C13.C3.C22.C$

68.C.C.C.C.C.C2.C9.C2.C6.C35.C6.C56.C.C15.2C9.C3.C21.C$53.2C.C5.C.2C

12.C9.C9.C2.C28.2C.C3.3C.C58.C20.C8.C13.C10.3C$78.C6.C.2C.C.3C4.3C17.

3C.C13.C2.3C.C56.C19.2C8.C5.C3.C2.C8.2C.2C$72.A16.3C6.C.C19.C2.C6.C

71.C.C.C16.C13.C10.C.C2.C$56.7C15.C11.C3.C42.2C66.4C14.C17.C2.C8.C$

86.C2.C4.C28.C14.C3.C61.C3.30C10.C2.13C.C$89.C31.C16.C102.C2.C$89.C

31.C7.A.A.A4.C68.C29.C6.C3.C.C$88.C148.C$138.C$125.C.C.C.C.C.C!Code: Select all

x = 154, y = 87, rule = Fireworld2

3$92.C$90.C.C16.C$58.C50.C$59.10C.2C17.C.2C16.C$65.C19.C19.C3.C$79.A.

A17.A9.C$60.2C.C21.C19.C3.C$68.C.2C13.C3.C.2C12.C3.C$75.C.C.C.C.C.C9.

C.C.C.C.C.C3.C$73.13C8.12C3.C$77.C3.C27.C$71.2C4.C3.C10.2C15.C$71.3C

3.C3.C10.3C14.C$71.3C3.C3.C10.3C14.C$67.C5.C4.C2.C6.C5.C14.C$67.C14.C

5.C20.2C$73.C11.C8.C14.C$67.C17.C2.C20.C$66.C8.C45.C.C$58.C9.C16.C20.

C2.C10.C2.C$68.C3.C2.C30.C20.C.C$58.C16.C12.C3.C3.C3.C5.C4.C2.C2.C2.

4C4.3C$55.C2.C6.C2.C2.C.4C10.C3.C3.C3.C4.C.C4.C15.C2.C$58.2C4.C2.C19.

C3.C3.C3.C14.C5.C2.C6.C$55.C2.C13.C4.C.C7.C3.C3.C3.C6.6C3.C5.C.C6.C$

55.C2.C15.2C3.C7.C3.C3.C3.C2.C7.C4.C14.C$55.C2.C10.C13.C3.C3.C3.C3.C

2.C3.C3.C3.C15.C$55.C11.13C4.16C7.C22.C$55.C2.C24.C3.C14.C7.C3.C2.C

12.C$55.C11.C11.C50.C$55.C12.C10.C50.C$55.2C35.C37.C$55.C34.C.C16.C

20.C$55.C2.C50.C20.C$55.C3.10C.2C17.C.2C16.C20.C$55.C9.C19.C19.C3.C

20.C$55.C23.A.A17.A9.C20.C$55.C4.2C.C21.C19.C3.C20.C$55.C12.C.2C13.C

3.C.2C12.C3.C20.C$55.C19.C.C.C.C.C.C9.C.C.C.C.C.C3.C20.C$55.C17.13C8.

12C3.C20.C$55.C21.C3.C27.C20.C$55.C15.2C4.C3.C10.2C15.C20.C$55.C15.3C

3.C3.C10.3C14.C20.C$55.C15.3C3.C3.C10.3C14.C20.C$55.C11.C5.C4.C2.C6.C

5.C14.C20.C.C$55.C11.C14.C5.C20.C20.2C.C6.C$55.2C16.C11.C8.C14.C20.C

2.C3.C2.C$55.C11.C17.C2.C20.C$55.C10.C8.C33.C21.3C2.C.3C$55.C2.C9.C

16.C7.2C11.C2.C$55.C12.C3.C2.C19.C10.C2.C20.C2.C3.C$55.C2.C16.C20.C

12.C20.2C.C$10.C44.C2.C6.C2.C2.C.4C16.2C.C.2C6.C2.C20.C.C$11.C43.C2.

2C4.C2.C41.C20.C$11.CA3.C41.C13.C4.C.C10.C18.C20.C$10.2BA42.C2.C15.2C

3.C10.C18.C20.C$11.C46.C10.C13.C21.5C20.C$67.13C4.7C7.C.C3.C25.C$58.C

24.C10.C6.C2.C25.C$67.C11.C17.C.2C3.C25.C$68.C10.C24.C25.C$104.2C24.C

$99.C.C2.C25.C$100.C3.C25.C$100.C3.C25.C$130.C$102.C27.C$99.2C.C.2C

24.C$130.C$130.C$130.C$101.C.C26.C$102.C27.C$101.2C27.C$102.29C!Code: Select all

x = 110, y = 52, rule = Fireworld2

9$66.C$64.C.C16.C$32.C50.C$33.10C.2C17.C.2C16.C$39.C19.C19.C3.C$53.A.

A17.A9.C$34.2C.C21.C19.C3.C$42.C.2C13.C3.C.2C12.C3.C$49.C.C.C.C.C.C9.

C.C.C.C.C.C3.C$47.13C8.12C3.C$51.C3.C27.C$45.2C4.C3.C10.2C15.C$45.3C

3.C3.C10.3C14.C$45.3C3.C3.C10.3C14.C$41.C5.C4.C2.C6.C5.C14.C$41.C14.C

5.C20.2C$47.C11.C8.C14.C$41.C17.C2.C20.C$40.C8.C45.C.C6.C$32.C9.C16.C

20.C2.C10.C2.C6.C$42.C3.C2.C30.C20.C$32.C16.C12.C3.C3.C3.C5.C4.C2.C2.

C2.4C4.3C$6.C25.C6.C2.C2.C.4C10.C3.C3.C3.C4.C.C4.C15.C$7.BA4.BA.C15.

2C4.C2.C19.C3.C3.C3.C14.C5.C2.C$6.CBA4.BA17.C13.C4.C.C7.C3.C3.C3.C6.

6C3.C5.C.C$6.CA24.C15.2C3.C7.C3.C3.C3.C2.C7.C4.C$5.C26.C10.C13.C3.C3.

C3.C3.C2.C3.C3.C3.C$41.13C4.16C7.C$32.C24.C3.C14.C7.C3.C2.C$41.C11.C$

42.C10.C!A note about asynchronous logic: unmatched data streams could be easily synchronized by storing them in registers and shooting them out synchronously after receiving all expected streams, thus eliminating timing issues even more. However, this would significantly slow down the computation. My CPU is self-synchronized by the data read from the RAM.

It's also possible to use pulsating logic for things like inverters by using an AND regulator for aligning p6 signals:

Code: Select all

x = 106, y = 70, rule = Fireworld2

10$52.A13.CB$51.B2C.C6.AC4.C2.C$51.C10.BC4.BA$56.BA5.A4.CA$46.C6.11C

5.C$62.C6.C$46.C6.C8.C5.C18.2C.C$46.C7.C$46.2C14.C5.C2.C$46.C9.A9.C

11.C$46.C8.B2C.C15.C3.AC2.C$46.C8.C19.C2.BA$46.C.C11.BA4.BA4.BA4.B.C$

46.3C8.19C5.C$46.C.C25.C6.C6.C.C.C$47.C9.C16.C5.C11.C$48.C9.C29.3C.C$

46.C27.C5.C2.C$46.2C18.C11.C$46.C5.2C.C7.C3.AC2.C$46.C4.CA2B8.C2.BA$

46.C.C3.4A4.BA4.B.C22.C.C$46.3C4.11C5.C23.C$46.C.C13.C6.C21.C$53.C8.C

5.C24.C$46.C.C5.C$43.C2.C15.C5.C2.C$19.C26.C10.BA7.C11.CB$18.2A4.BA3.

C16.C9.2CAC14.AC4.C2.C$18.BC4.BA20.C8.C18.BC4.BA$19.C26.C15.BA4.BA5.A

4.CA$19.C23.C2.C.C8.19C5.C4.C$19.C54.C6.C4.C2.2C.C$19.CB25.C.C8.C16.C

5.C5.C5.C$18.CA26.3C9.C27.C3.C.C$46.C.C25.C5.C2.C$46.C5.A13.CB10.C7.C

$46.C4.B2C.C6.AC4.C2.C$46.C4.C10.BC4.BA$46.C9.BA5.A4.CA19.2C.C$46.C.C

4.11C5.C22.C$62.C6.C$46.C.C4.C8.C5.C$46.3C5.C$46.C.C13.C5.C2.C$46.C

19.C11.C$46.C8.A2C.C15.CB3.C2.C$46.C8.CB18.C.BA$46.2C8.4BA4.BA4.BA4.B

A.C8.2C.C$46.C10.19C5.C$46.C27.C5.BCB$57.C16.C5.C$46.C11.C$74.C5.C2.C

$78.C!Such a regulator is also used to detect the right moment for accessing the rotating memory segments. It reads p3 sequences from a 6-bit register that read p6 data and converts them to pulsating p3 bytes (with 2 trailing zeros). These bytes are then xored with a clock that produces a constant stream of increasing bytes. When the match is found, another clock initiates an r/w memory cycle. The RAM is in principle byte-accessible and could even be made bit-accessible.

I only use simple regulators for single trigger signals pulsating at p24:

Code: Select all

x = 35, y = 32, rule = Fireworld2

6$26.CA$26.B2C.C3$28.2B.C$28.3A$31.C2$28.A2.C2$25.C$23.3C3.A.C$4.BA$

4.BA17.C.C$28.2C$28.2C2$22.C.2C3$25.2C.C$27.C$28.C$28.C!

Code: Select all

x = 41, y = 41, rule = Fireworld2

4$30.C$31.5C.C$33.AB$35.2B$35.2A11$35.2B$7.C$15.BA10.BA7.A.C$7.C7.BA

10.BA$7.C$6.AC27.2C$6.BC27.2C$7.C$6.C4$35.2B$35.2A5$36.C!

[5-bit column number][5-bit row number][6-bit address of the actual pulsating 32-bit word]

Read/write cycles are triggered when 2 p3 streams of 32 bits, sent to the right column and the right row, match each other inside the RAM grid by an AND gate. AND gates don't work properly with arbitrary p3 data (p4 seems to be the absolute minimum for simple AND gates). Nevertheless, they do work for detecting and receiving 2 identical data streams. The memory requires only XOR, NOT, a temporary lock for filtering out the pilot bit and a simple data extraction mechanism that reads 47-48 bits. The unwanted trailing bits are later cut upon reading the data and converting it into a 32-bit p6 stream. All this works well with p3, as well as the display, although in order to make the pixel detectors smaller I use a crude flip-flop mechanism that produces annoying frame refresh lines on the screen. I would like to improve it, if I find a clean flip-flop of the same or smaller size capable of operating at p3.